| Jewiki unterstützen. Jewiki, die größte Online-Enzyklopädie zum Judentum.

Helfen Sie Jewiki mit einer kleinen oder auch größeren Spende. Einmalig oder regelmäßig, damit die Zukunft von Jewiki gesichert bleibt ... Vielen Dank für Ihr Engagement! (→ Spendenkonten) |

How to read Jewiki in your desired language · Comment lire Jewiki dans votre langue préférée · Cómo leer Jewiki en su idioma preferido · בשפה הרצויה Jewiki כיצד לקרוא · Как читать Jewiki на предпочитаемом вами языке · كيف تقرأ Jewiki باللغة التي تريدها · Como ler o Jewiki na sua língua preferida |

AMD Bulldozer

Bulldozer ist eine von AMD entwickelte Mikroarchitektur für x86-Prozessoren mit 64-Bit-Erweiterung und Nachfolger von AMD K10. Erste Prozessor-Modelle auf Bulldozer-Basis wurden unter dem Markennamen AMD FX im Oktober 2011 vorgestellt. Das wichtigste Architekturmerkmal ist das sogenannte „Core Multithreading“ (CMT), einige Elemente wurden aber auch aus der AMD-K10-Architektur übernommen.[1] Die Bulldozer-Architektur inklusive der Optimierung Piledriver wird von der Steamroller-Architektur abgelöst.

Architekturmerkmale

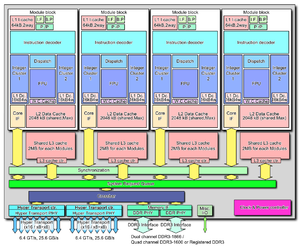

Der komplett neu entwickelte Bulldozer ist AMDs größte Mikroarchitekturveränderung seit der Einführung von AMD64 im Jahre 2003. Bulldozer basiert im Unterschied zu AMD K10 auf Modulen. Ein Modul hat zwei 128-Bit-Gleitkommaeinheiten (FPUs), die bei Bedarf zu einer 256-Bit-breiten Gleitkommaeinheit kombiniert werden können. Der FPU stehen pro Modul zwei Integercluster mit je zwei ALUs und zwei AGUs („adress generation units“) zur Seite. Pro Modul gibt es einen von allen Einheiten des Moduls geteilten L2 Cache. Betriebssysteme erkennen ein Modul als zwei logische Prozessorkerne. Ein Bulldozer-Die beherbergt maximal vier Module. Damit können maximal acht Threads gleichzeitig abgearbeitet werden. Der größte Bulldozer-Ableger (Interlagos) setzt sich aus zwei Siliziumplättchen zusammen und kommt mit seinen 16 Threads nicht ganz an den zu der Zeit größten Intel Xeon (Haswell-EP) heran, der mit max. 18 Kernen und Hyper-Threading auf 36 Threads kommt.[2][3][4][5]

Modul

Die von AMD bei Bulldozer eingeführte Clustered-Integer-Core-Architektur wurde ursprünglich von DEC entwickelt und erstmals 1996 mit der RISC-CPU Alpha 21264 vorgestellt.

Das Modul ist ein Kompromiss zwischen echtem Dualcore, wo jedem Thread alle Funktionseinheiten des Prozessorkerns zur Verfügung stehen, und einem Singlecore mit Simultaneous Multithreading (SMT). Das Konzept spart Fläche im Vergleich zum gewöhnlichen Dualcore. Ein Modul ist in verschiedene einfach und doppelt vorhandene Einheiten aufgeteilt, die sich zudem manche Ressourcen teilen. Es hat zwei Integer-Einheiten (Ganzzahl) und eine 256-Bit-Floatingpoint-(Gleitkommazahl)-Einheit, die bei Bedarf in zwei 128-Bit-FPUs aufgeteilt werden kann. Die Fetch-und-Decode-Einheit sind ebenfalls nur einfach vorhanden und teilen die Last auf die jeweiligen Einheiten auf. Ein Modul verfügt über einen 2-MB-Shared-L2-Cache, einen 16-kB-4-Wege-L1-Datacache pro Integercluster und einen 64-kB-2-Wege-L1-Instructionscache. Die beiden unabhängigen Integercluster sind jeweils mit zwei ALUs und zwei AGUs ausgestattet, was maximal vier Arithmetik- und Speicheroperationen pro Modul und Takt erlaubt.[6] Jedes Modul besitzt zwei symmetrische 128-Bit-FMAC-Gleitkommapipelines, die bei Bedarf in eine 256-Bit-breite Einheit umfunktioniert und damit für einen FMA-Befehl verwendet werden können. FMA rundet anders als der Multiply-Add-Befehl erst nach Ende der kompletten Berechnung das Ergebnis. Alle Module einer CPU teilen sich den ggf. vorhandenen L3-Cache sowie das Dual-Channel Interface.

Befehlssatzerweiterungen

AMD unterstützt mit der Bulldozer-Mikroarchitektur diverse Instruktionen wie Intels AVX („Advanced Vector Extensions“), SSE4.1, SSE4.2, AES, CLMUL, als auch von AMD entwickelte Instruktionen (XOP, FMA4). Das von AMD entwickelte 3DNow! fällt mit dieser Generation erstmals weg.[7]

Implementierung

Mikroprozessoren auf Bulldozer-Basis wurden 2011 von AMD zunächst nur in der „Enthusiasten“-Serie (als AMD FX) und im Serverbereich (als AMD Opteron) in den Markt eingeführt. Für die Verwendung in Servern werden sowohl CPUs mit zwei Dies unter einem Integrated Heatspreader (IHS) mit dem Codenamen Interlagos (bis zu 16 Threads) auf dem Sockel G34 vertrieben, als auch CPUs mit einem Die unter dem IHS mit dem Codenamen Valencia (4 bis 8 Threads) auf dem Sockel C32. Diese sind, anders als bei den Consumer Versionen, als LGA-CPUs konzipiert. Alle bisherigen CPUs auf Bulldozer-Basis, einschließlich der aktuellen Piledriver-Revision, werden bei GlobalFoundries im 32-Nanometer-SOI-HKMG-Verfahren gefertigt. Ein Modul des Orochi-Dies, das die Basis für CPUs der Typen Zambezi (FX-Serie) und Valencia (Opteron-Serie) bildet, beinhaltet auf einer Fläche von 30,9 mm² ca. 213 Millionen Transistoren.

Piledriver

Piledriver heißt die erste Überarbeitung von AMDs Umsetzung der Clustered-Integer-Core-Architektur. Sie wurde im Jahr 2012 vorgestellt und sollte in allen Anwendungsbereichen Einzug halten: im Server-Segment weiterhin als Opteron, im APU-Segment unter dem Codenamen Trinity und sowie als Ersatz für die erste Generation der FX-CPUs.

Neben Verbesserungen bei der Sprungvorhersage und der Auslastung der Pipelines wurden folgende Neuerungen eingeführt:[8]

- Unterstützung von FMA3, welches von Intel erst mit der Haswell Architektur eingeführt wurde

- Instruktionen zur Bit(masken)manipulation: BMI1 (Intel-kompatibel) und TBM (AMD-spezifisch)

- Unterstützung für Gleitkommazahlen halber Genauigkeit: F16C

- Überarbeiteter und schnellerer L2-Cache

- Neue Clock-Mesh (nur bei Trinity-Version)

- Doppelt so großer Level 1 TLB für Daten (64 statt 32 Einträge)

Neben Trinity basiert auch das 2013 vorgestellte Prozessor-Stepping Richland auf Piledriver-CPU-Kernen.

Einzelnachweise

- ↑ Die Bulldozer-Architektur, Artikel zum offiziellen Start der Prozessoren. In: ht4u.net

- ↑ http://www.tomshardware.de/AMD-Interlagos-Opteron-Bulldozer-ISC-2011,news-245877.html

- ↑ Archivlink (Memento vom 20. Oktober 2014 im Internet Archive)

- ↑ https://www.heise.de/newsticker/meldung/Xeon-Prozessor-mit-18-Kernen-2235856.html

- ↑ http://ark.intel.com/products/81061/Intel-Xeon-Processor-E5-2699-v3-45M-Cache-2_30-GHz

- ↑ http://www.computerbase.de/artikel/prozessoren/2011/test-amd-bulldozer/8/#abschnitt_back_end

- ↑ http://www.computerbase.de/artikel/prozessoren/2011/test-amd-bulldozer/9/#abschnitt_avx_aes__co

- ↑ http://www.tomshardware.de/a10-4600m-trinity-APU-piledriver-Test,testberichte-241025-2.html

Weblinks

- Bulldozer-Architektur unter der Lupe: Schwachstellen identifiziert. In: Planet 3DNow!

- The Bulldozer Aftermath: Delving Even Deeper. In: AnandTech

Vorlage:Navigationsleiste AMD-Prozessoren

| Dieser Artikel basiert ursprünglich auf dem Artikel AMD Bulldozer aus der freien Enzyklopädie Wikipedia und steht unter der Doppellizenz GNU-Lizenz für freie Dokumentation und Creative Commons CC-BY-SA 3.0 Unported. In der Wikipedia ist eine Liste der ursprünglichen Wikipedia-Autoren verfügbar. |